- Parasitic Extraction 및 Metal Layer Stack Rc Extrac

- Vlsi Cad Rents Rule이란

- 싱가포르 여행기 뉴턴 맥스웰 호커 푸드 센터

- 내가 보려고 만든 반도체 자료 모음집 반도체 검색 꿀팁

- 2025 신년사 반도체로 빛나는 대한민국의 새 아침

- 과학기술정책 Bio Tech 곧 Gdp 대비 의료비 20 비율의 시대가 옵니다

- 과학기술조직론 과학기술 스타트업 창업 후 운영 방안

- 제 2차 세계대전과 미국의 과학기술 발전 Mit Rad Lab 오펜하이머 Los Alamo

- 과학기술조직론 Team Building

- 부자와 Stem 엘리트들 한국 탈출 이유

디지털 반도체 설계 엔지니어들은 회사에서 무엇을 할까?

스마트폰, 자동차, 가전제품 등 어느 것을 보더라도 그 안에는 작은 칩 하나가 모든 것을 가능하게 합니다.

그런데 이 칩을 설계하고 구현하며 검증하는 사람들은 어떤 하루를 보낼까요?

반도체 업계에 관심을 가진 여러분을 위해, 주요 직무인 RTL 디자이너, Verification 엔지니어, DFT 엔지니어, PD 엔지니어, 그리고 아날로그 엔지니어의 하루를 소개합니다.

그냥 재미로 가볍게 써봤습니다. 분명 아쉬운 내용들이 있을텐데, 댓글에서 알려주세요. 본문 업데이트 하겠습니다.

- RTL Engineer: 디지털 회로 설계의 시작

RTL Engineer란?

RTL(Register Transfer Level) 엔지니어는 디지털 회로의 설계를 시작하는 사람들입니다. 이들의 작업은 회로의 기능을 정의하고, HDL(Hardware Description Language)로 이를 구현하는 것에서 시작됩니다.

RTL Designer의 하루: 설계의 첫걸음을 책임지는 사람들

RTL(Registered Transfer Level) Designer는 반도체 설계의 핵심을 만드는 엔지니어입니다. 우리가 개발하는 코드 한 줄 한 줄이 칩의 뼈대를 형성하고, 최종 제품의 성능과 기능을 좌우합니다.

어떤 회사는 RTL 엔지니어가 A-to-Z로 다 하는 것 같습니다. 다 한다는 의미는,

(1) Matlab, System C로 알고리즘부터

(2) FPGA 설계도 하고,

(3) IP 코어 설계도 하고,

(4) 문서도 만들고

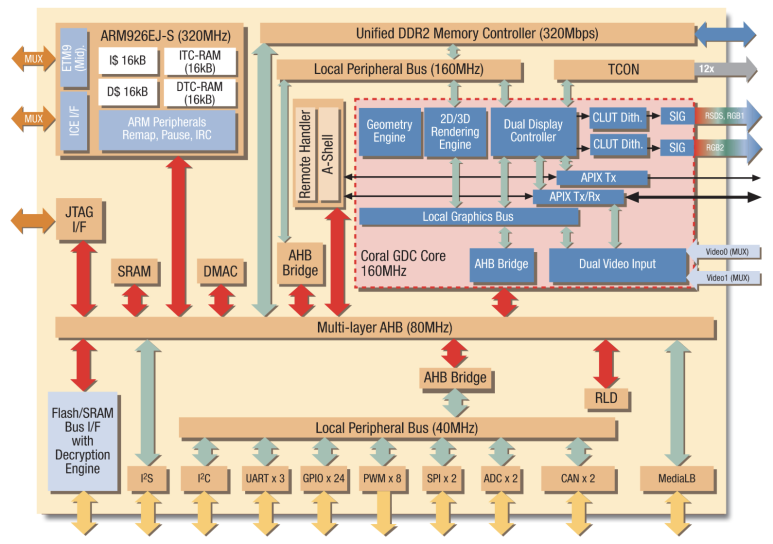

(5) SoC Integration도 하고,

(6) Logic synthesis에 사용할 SDC 만들고, UPF도 만들고

(7) Logic Synthesis 하고

(8) Lint도 잡고

(9) SDC Clean도 하고…

(10) 아, 테스트벤치도 만들고…

(11) 갑자기 회사 정책이 바뀌어서, Chisel, PLI, VPI, C/C++ 등 다른 언어를 쓰겠다고 하면 그거로 갈아탈 준비를 해야하고…

위 작업들이 어떤 회사는 담당하는 엔지니어가 따로 있고… 어떤 회사는 RTL엔지니어가 다 하는 업무입니다.

- 사양(Spec)과의 씨름

스펙 읽기: 고객이 요구하는 기능과 시스템의 전반적인 요구사항이 담긴 사양서를 꼼꼼히 읽습니다.

스펙 이해하기: 사양의 핵심을 파악하고, 구현 가능한 설계로 변환할 수 있는 방법을 고민합니다.

스펙 관련 질문 정리: 설계팀, 시스템팀, 혹은 고객에게 물어볼 질문들을 정리해 명확하게 소통합니다.

- 설계와 코드 작성

RTL 코딩: Verilog나 SystemVerilog 같은 언어로 하드웨어 동작을 정의하는 코드를 작성합니다.

코드 시뮬레이션: 작성한 코드가 예상대로 작동하는지 기본적인 시뮬레이션 툴을 이용해 테스트합니다.

설계 구조 최적화

- 협업: 팀원들과 소통

설계 리뷰: 팀원들과 코드 리뷰를 진행하여 설계가 올바른 방향으로 가고 있는지 확인합니다.

크로스팀 미팅: Verification 팀이나 Physical Design 팀과 협력하며, 설계에서 고려해야 할 사항을 논의합니다.

피드백 반영

- 문제 해결: 디버깅과 수정

시뮬레이션 디버깅: 시뮬레이션 중 발견된 문제를 분석하고 수정합니다.

툴 활용하기: 업계 표준 EDA 툴(예: Synopsys VCS, Cadence Xcelium)을 사용하여 다양한 시뮬레이션을 실행합니다.

버그 추적 및 수정: 그리고 PD Engineer에게 아쉬운 소리를 합니다. 진짜 죄송한데 FECO 한번만…

- 학습과 발전

새로운 기술 트렌드 공부: 최신 논문, 블로그, 업계 세미나 자료 등을 통해 새로운 설계 기술을 학습합니다.

기존 설계 재검토: 현재 진행 중인 설계를 다시 살펴보며 개선점을 찾습니다.

멘토링: 주니어 엔지니어들에게 조언하며 기술적인 성장에 도움을 줍니다.

- 스크립팅과 자동화

스크립트 작성: 반복적인 작업을 줄이기 위해 Perl, Python 같은 언어로 스크립트를 작성합니다.

자동화 도구 활용: 시뮬레이션 실행, 결과 수집, 로그 분석 등 자동화된 툴을 활용해 생산성을 높입니다.

- 장기적인 목표와 협업

IP 모듈 통합: 자신이 설계한 RTL 블록을 다른 팀의 블록들과 통합하며 시스템 전체의 조화를 이룹니다.

파이프라인 검증: 설계가 전체 데이터 플로우에 적합한지 확인하고, 필요시 수정합니다.

성능 최적화: 성능 병목 현상을 줄이기 위한 설계 최적화 작업을 진행합니다.

설계의 첫 단추.

RTL Designer의 하루는 설계의 시작부터 끝까지 모든 단계를 책임지며, 팀과의 협업 속에서 성장과 도전을 반복합니다.

SVP를 위해 매우 중요한 RTL Freeze입니다.

- Design Verification Engineer: 설계의 기능 보증

Verification 엔지니어란?

Verification 엔지니어는 설계된 회로가 의도대로 작동하는지 확인합니다. 이들은 설계의 ‘기능 보증’ 역할을 하며, Test coverage를 높이는 것에 초점을 둡니다.

2010년? 2015년?쯤부터 DV쪽에 많은 수요가 발생한 것 같습니다. 굉장히 어렵구요.

Verification Engineer의 하루:

여기도 뭐 RTL 엔지니어처럼 회사by회사로 다른 것 같긴한데,

일부 회사에서는 “검증엔지니어(긴급 상황시에는 설계 땜빵)”처럼 일하는 경우도 있는 것 같습니다.

- Spec 읽기

(1) 설계 스펙을 읽고 이해합니다. Specification은 설계가 어떻게 작동해야 하는지 설명하는 ‘설명서’ 같은 것이죠.

(2) 다른 Spec도 읽기: 하드웨어 설계는 다양한 IP로 구성되므로, 관련된 모든 사양을 읽는 데 시간이 꽤 걸립니다.

(3) 더 많은 사양 읽기:네… 읽어야 할 문서 줄어드는 속도보다, 새롭게 할 일이 더 빠르게 만들어져요. 😂

- 설계 분석

(1) 설계 공부: 현재 검증 중인 회로 블록의 설계 구조를 파악합니다.

(2) 더 깊이 공부: 그냥 끝이 없는 느낌. ㅠㅠ

- 계획 및 조율

(1) 계획 세우기: 어떻게 테스트를 진행할지 전략을 수립합니다.

(2) 계획 다시 점검: 현실(일정, 내가 투자 할 수 있는 시간, 컴퓨팅 리소스)과 계획 사이의 간극을 메우기 위해 계획을 수정합니다.

- 협업: 보고와 문서화

Weekly/Daily meeting: 현재 진행 상황과 문제를 팀원들에게 공유합니다.

타 부서와 미팅: Verification은 설계팀, DFT팀 등 다양한 팀과 협력해야 하기 때문에 크로스팀 회의가 필수입니다.

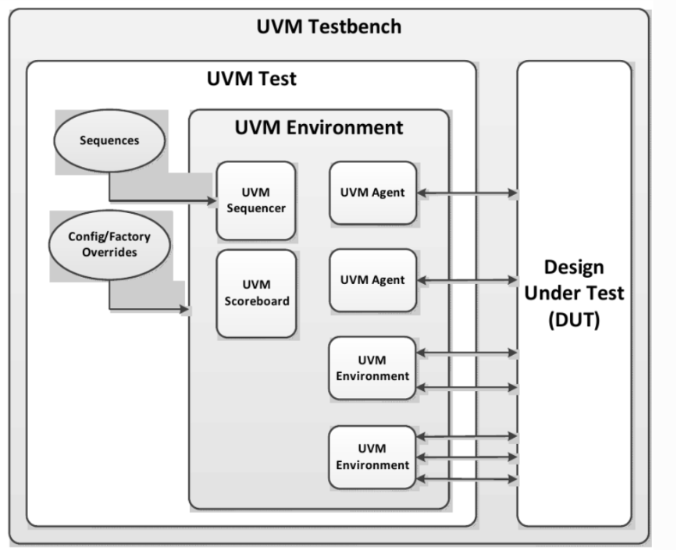

테스트벤치 아키텍처 문서 작성: 테스트 환경의 구조를 설명하는 문서를 작성합니다.

- 멘토링과 개선

주니어 멤버 멘토링: 경험이 적은 팀원들에게 도움을 주고, 기술적으로 지도합니다.

검증 방법론 개선 제안: 효율적인 검증 방법을 찾아 프로세스를 개선합니다.

- 학습과 코드 리뷰

DVCon 논문 읽기: DVCon이나 기타 업계 컨퍼런스의 논문을 읽으며 최신 트렌드를 파악합니다.

코드 리뷰: 다른 팀원이 작성한 코드를 검토하여 개선점을 제안합니다.

https://dvcon.org/

- 디버깅과 스크립팅

RTL 디버깅: RTL(Register Transfer Level) 설계의 버그를 분석하여 문제를 해결합니다.

스크립트 작업: 작업 자동화를 위한 스크립트를 작성합니다.

- 테스트 작성 및 환경 설정

테스트 및 시퀀스 작성: 설계의 특정 동작을 검증하기 위한 테스트를 작성합니다.

테스트벤치 구성 요소 작성: 테스트 환경에 필요한 모듈과 기능을 구현합니다.

- EDA/IP 회사에 질문 올리기

이거 버그 같은데…. 이거 잘못 만든거같은데… 여기서 Tool crash 발생함…

- 팀즈/아웃룩 쳐다보다가 멍해지기

CI 파이프라인 감상

작성한 코드가 CI 파이프라인에서 테스트되는 과정을 지켜보기

- DFT 엔지니어: 테스트 가능성을 설계하는 마스터

DFT 엔지니어란?

DFT(Design for Testability) 엔지니어는 반도체 칩의 제조 후에 발생 될 수 있는 결함 테스트를 용이하게 만드는 설계를 담당합니다. 이들의 역할은 칩의 수율을 보증하는 데 매우 중요합니다.

DFT Engineer의 하루: 설계 품질을 보증하는 숨은 영웅들

DFT(Design For Testability) Engineer는 반도체 설계 과정에서 칩의 테스트 가능성을 설계하는 전문가입니다.

이 R&R도 회사 By 회사입니다.

DFT 넣고 ATPG까지만 하는 회사도 있고,

DFT 스펙 정하는 것부터 시작해서, DFT용 STA SDC까지 Hands on 하는 회사가 있고,

VCS & Verdi 등 사용해서 Pre/Post Gate level simulation까지 하는 회사가 있고,

실제 칩 나오면 보드 꾸며서 Low Frequency clock 넣어서 Stuck at fault 정도 Testing까지 하는 회사도 있고,

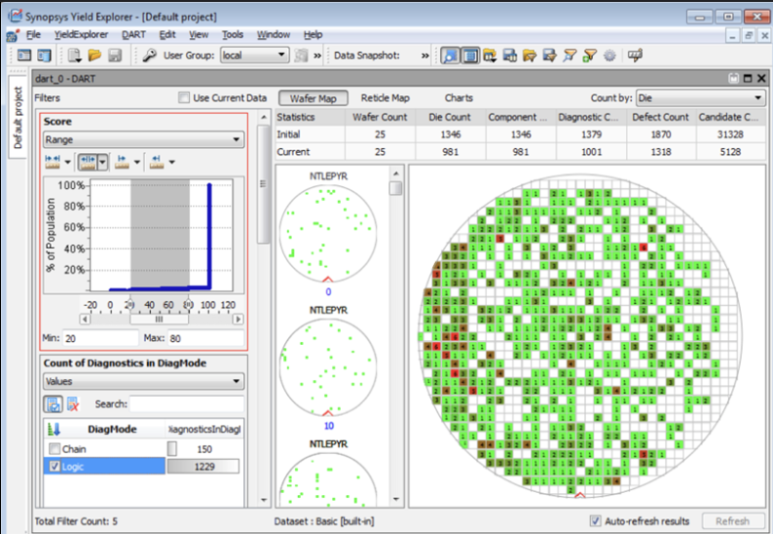

ATE Testing 옆에 붙어서 Diagnosis 분석까지 하는 회사도 있고,

Silicon이랑 Design이랑 차이 분석까지 하는 회사도 있고,

P&R 단계에 SCAN Restructure / Re-ordering까지 봐줘야 하는 회사도 있고…….

- 아침: 사양서와의 만남

사양 읽기 및 분석: 고객의 요구사항과 설계팀이 제공한 RTL의 구조를 바탕으로 테스트 전략을 계획합니다.

테스트 요구사항 파악: 어떤 테스트가 필요한지, 테스트 커버리지를 어떻게 확보할지 고민하며 목표를 설정합니다.

질문 정리 및 협의: 설계팀과 Verification 팀과 협력하며 테스트 전략과 설계 제약 조건에 대해 논의합니다.

- 테스트 아키텍처 설계

스캔 체인 삽입 계획: 칩 내부에 테스트를 위한 스캔 체인을 배치할 방법을 설계합니다.

BIST (Built-In Self Test) 설계: 칩 자체에서 테스트를 수행할 수 있는 로직(BIST)을 설계하고 삽입합니다.

SCAN Insertion, Stitching 및 검증: RTL 설계에 DFT 로직을 삽입하고, 추가된 로직이 전체 설계에 문제를 일으키지 않는지 확인합니다.

- 협업과 문제 해결

크로스팀 협력: RTL Designer, Verification Engineer, Physical Design Engineer와 협력하여 DFT 삽입 과정에서 발생하는 제약 사항을 해결합니다.

디버깅 및 분석: 시뮬레이션 결과에서 발견된 오류를 분석하고, 문제의 원인을 찾아 수정합니다.

대충 이런 시나리오:

DFT: 진짜 죄송한데 FECO 한번만… 이 pin disconnect 하고 여기 MUX에 넣으면 되는데요…..

PD: 아니 그거 넣으려면 위치 고려해서 넣어야하고, Skew 안맞아서,, 타이밍이 어쩌구 Legalize 다시해야하고 PV 다시해야하고 어쩌구 저쩌구…

테스트 패턴 협의: 테스트 패턴 생성 및 적용에 대한 내용을 제조사(Foundry)와 협의합니다.

- 테스트 패턴 생성

ATPG (Automatic Test Pattern Generation): DFT 소프트웨어를 사용해 결함을 찾아낼 수 있는 최적의 테스트 패턴을 생성합니다.

결함 커버리지 분석: 생성된 테스트 패턴이 설계의 모든 영역을 충분히 테스트할 수 있는지 분석합니다.

패턴 최적화: 테스트 시간이 짧고 효율적인 패턴을 찾기 위해 최적화를 진행합니다.

- 도구와 스크립팅 활용

EDA 툴 활용: Synopsys Testmax, Mentor Tessent, Synopsys YieldExplorer 같은 DFT 전용 도구를 사용하여 테스트를 자동화합니다.

스크립트 작성 및 개선: 테스트 데이터 처리, 결과 분석 등의 작업을 자동화하기 위해 Python, Tcl 같은 스크립트 언어로 작업합니다.

- 검증과 리포트

결과 검토: 테스트 결과를 분석하여 테스트 커버리지가 부족한 부분을 찾아냅니다.

리포트 작성: Block 별 진행 상황, 결함 커버리지, 개선 방향 등을 정리해 팀과 공유합니다.

- 학습과 멘토링

최신 기술 트렌드 학습: DFT 관련 최신 논문, 세미나, 기술 문서를 읽으며 새로운 방법론을 배웁니다.

주니어 멘토링: 새로운 팀원들에게 DFT의 기본 개념과 도구 사용법을 설명하며 기술적인 성장을 돕습니다.

프로세스 개선 제안:팀의 효율성을 높이기 위한 개선 아이디어를 제안합니다.

- 하루 마무리와 목표 설정

오늘의 성과 정리: 테스트 패턴 생성, 문제 해결, 협업에서 얻은 결과를 기록합니다.

내일의 계획 세우기: 오늘 해결하지 못한 문제에 대한 Action Item을 정리합니다.

- Physical Design (PD) 엔지니어: 논리적 설계를 물리적인 설계로.

PD Engineer의 하루: 칩 설계의 마지막 퍼즐을 완성하다

PD(Physical Design) Engineer는 RTL 설계를 실제 칩 형태로 구현하는 전문가입니다. 우리가 만든 설계는 전자의 흐름을 최적화하고, 칩의 성능, 전력, 면적 요구사항을 충족시키기 위해 중요한 역할을 합니다. PD Engineer의 하루는 디지털 설계의 구체화를 위한 정교한 작업들로 가득 차 있습니다.

- 아침: 설계 이해와 목표 설정

사양서 검토: RTL 팀으로부터 받은 설계의 논리적 구조를 이해하고, 주요 요구사항과 제약 조건을 파악합니다.

PPA (Performance, Power, Area) 목표 정의: 성능, 전력 소비, 면적을 최적화하기 위한 구체적인 목표를 세웁니다.

초기 검토 및 협의: 타 팀(DFT, Verification 등)과 협력해 설계의 전반적인 흐름과 Constraint를 논의합니다.

- 설계 데이터 준비

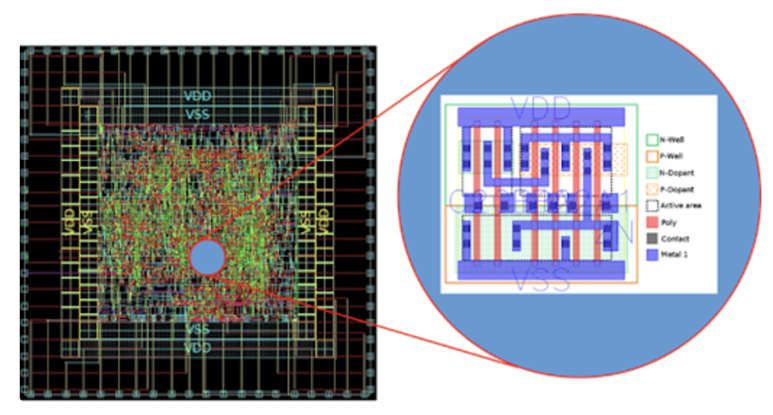

RTL-to-GDSII 흐름 설정: 논리 설계를 실제 실리콘 레이아웃으로 변환하는 전체 플로우를 설정합니다.

기본 라이브러리 준비: Standard Cell, Memory Macro, I/O Pad 등의 데이터베이스를 확인하고 초기 환경을 설정합니다.

제약 파일 작성: 클럭, 리셋, 타이밍 제약 등의 제어 파일(SDC)을 작성하여 설계의 요구사항을 반영합니다.

- 배치와 라우팅 (Placement & Routing),

Floorplanning: 칩의 주요 블록을 효율적으로 배치

FEOL 배치, BEOL 연결

전원 및 클럭 설계

- 타이밍 및 검증

STA (Static Timing Analysis): 전체 설계의 Timing/Power를 분석하여, 물리적인 스펙에 만족하도록 합니다.

DRC/LVS 검증: DRC(Design Rule Check)와 LVS(Layout Versus Schematic)를 통해 설계가 제조 공정 규칙을 따르는지 확인합니다.

전력 분석 (Power Analysis): 전력 소비를 분석하고, 전력 효율을 높이기 위한 전략을 수립합니다.

EM/IR 분석: 전자기적 간섭(EM)과 전압 강하(IR)를 분석하여 전원 신호의 안정성을 보장합니다.

위 검증이 통과 되어야 칩이 동작을 합니다.

- 문제 해결과 협업

디버깅 및 수정: 타이밍 위반, 전력 문제, 배치 오류 등을 발견하고 해결합니다.

EDA 도구 활용: Synopsys ICC2, FC, Cadence Innovus 등 최첨단 툴을 사용하여 작업을 자동화하고 효율성을 높입니다.

크로스팀 협력: RTL, DFT, Verification 팀과의 지속적인 논의를 통해 설계 품질을 개선합니다.

- 설계 최적화

PPA 트레이드오프: 성능, 전력, 면적의 균형을 맞추기 위해 반복적으로 설계를 조정합니다.

Engineering Change Order: 설계 변경 사항(ECO)을 반영하며, 마지막 디테일까지 완성도를 높입니다.

성능 분석: 설계가 초기 목표를 얼마나 달성했는지 분석하고, 추가 개선 작업을 계획합니다.

- 최종 단계: GDSII 생성

최종 레이아웃 생성: GDSII 파일을 생성하여 실제 제조에 사용할 설계 데이터를 완성합니다.

테이프아웃 준비: 제조사(Foundry)에 설계 데이터를 전달하기 전, 모든 검증을 완료합니다.

결과 보고: 설계 과정과 결과를 문서화하고 팀 및 고객과 공유합니다.

여기서 끝나면 다행인데, 문제가 있으면 BEOL 공정 시작하기 전에 Metal ECO해서 Foundry에 BEOL 회로도를 새롭게 업데이트해서 다시 보내야합니다.

- 학습과 성장

최신 기술 습득: 논문, 세미나, 업계 동향을 통해 최신 PD 기술을 공부합니다.

멘토링: 주니어 엔지니어들에게 설계 경험과 노하우를 공유하며 팀의 성장을 돕습니다.

프로세스 개선 제안: 설계 플로우를 더욱 효율적으로 만들기 위한 새로운 아이디어를 제시합니다.

- 하루 마무리: 새로운 도전을 위해

성과 정리: 오늘 해결한 문제와 남은 과제를 정리하여 업무의 연속성을 유지합니다.

내일의 계획 세우기: 효율적인 진행을 위해 우선순위를 고려하며 내일의 목표를 설정합니다.

소소한 여유: 팀원들과 가벼운 대화를 나누며 긴 하루를 마무리합니다.

재미로+ 참고로 써봤습니다.

분명 제가 부족한 내용들이 있을텐데 댓글에서 알려주시죠. ㅎㅎ

해시태그 :

VLSI Wiki

VLSI Wiki