-

DC(dc_shell) - WLM 사용하는 Synthesis (미세공정에선 사용 힘듬.)

-

ZWLM - Zero wire load model. 런타임이 가장 빠름.

-

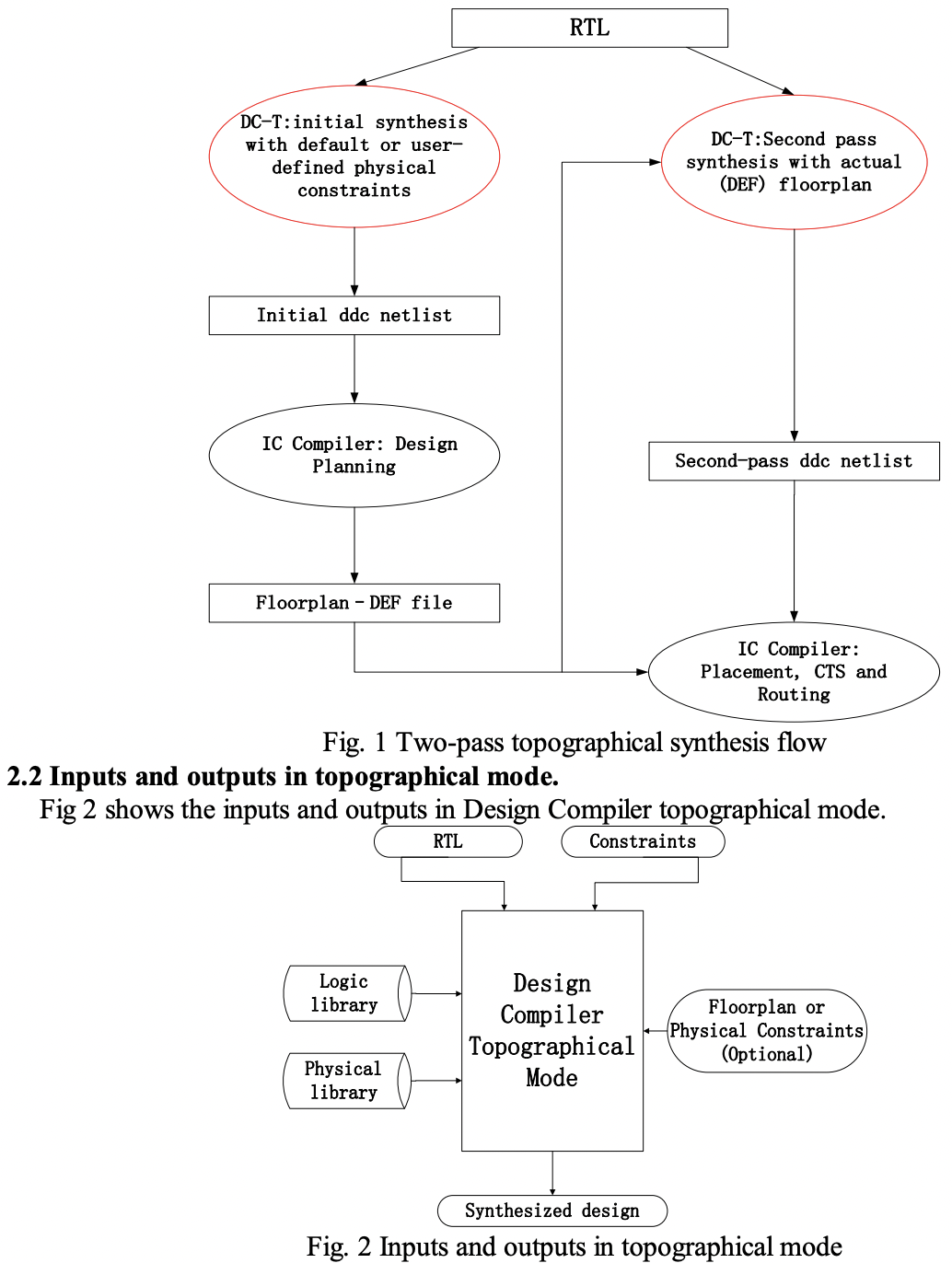

DCT(dc_shell -topographical) - 가상의 Floorplan을 통해 DEF 갖고 Wire 값을 좀 더 실제적으로 Synthesis

-

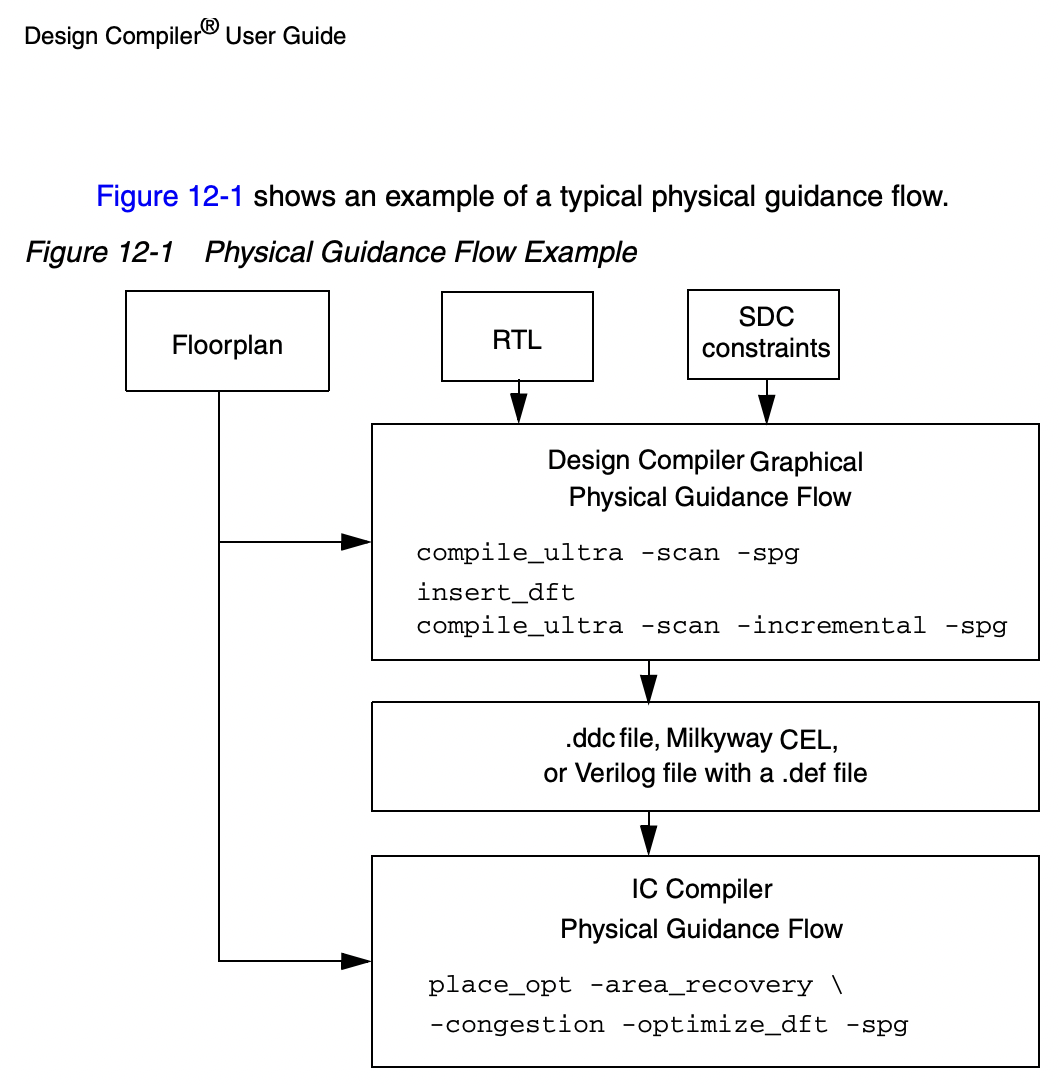

DCG(compile_ultra -spg) - 마지막 목표. ICC2를 이용해 실제적인 배치 후, 실제 DEF를 갖고 Synthesis

미세공정 디자인에서 DCG가 정확도는 제일 높은데, Ultra License를 사용할 수 있는 환경이어야 합니다.

Synopsys의 Design Compiler는 HDL에 대한 Synthesis를 할 수 있는 대표적인 EDA Tool입니다.

Synthesis 이후에 Timing과 Area를 확인할 수 있습니다.

Design이 미세공정으로 갈 수록, Gate에 대한 Delay보다 Net에 대한 Delay가 커집니다.

Gate에 대한 Delay는 Vendor에서 제공하는 Library File(.lib, .db)로 확인 할 수 있습니다.

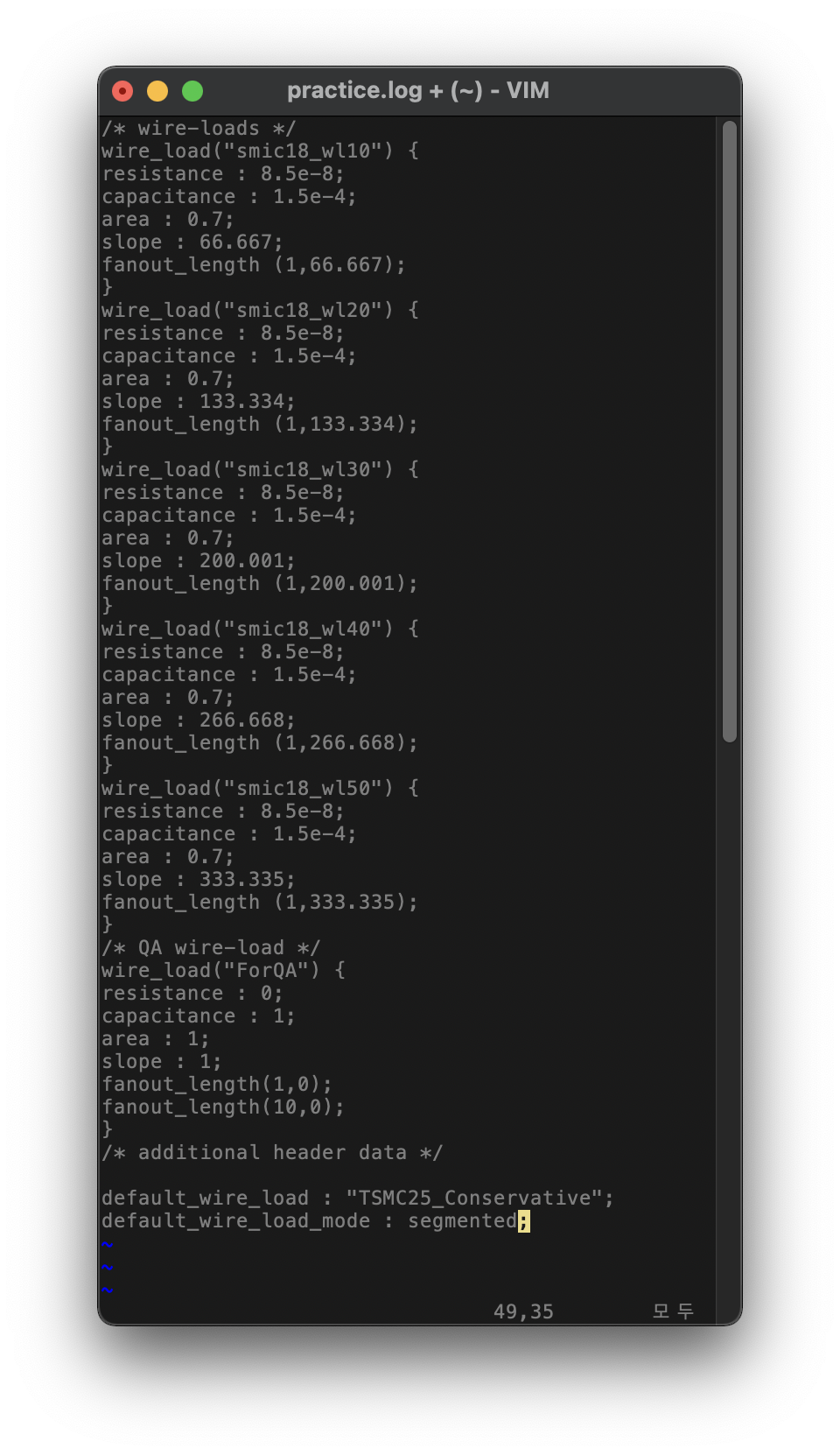

Wire에 대한 Delay의 경우, 0.35um이상의 공정에서는 Wire Load Model이라는 파일을 사용했습니다.

- WLMS : ‘Design의 Area가 8000이하라면, Wire의 RC값 Delay는 x값 정도로 지정할게요.’ 이런 식으로 통계적으로 계산되어있습니다.

0.18um이하의 공정으로 가면서 Net에 대한 Delay를 그냥 통계적으로는 둘 수가 없게 되었고, 새로운 방법이 필요해졌습니다.

그래서 나온 방법이 Custom WLM과 Physical Synthesis 등인데, 이후에 Topographical mode로 통합되었습니다.

- Topographical Mode : Default mode로 Synthesis 후, ddc로 저장하고, 가상의 Floorplaning을 통해 DEF파일을 갖고, 배선 정보를 갖고 topographical Synthesis를 하는 것입니다.

ref : Using Design Compiler Topographical Technology for Modern Process

Qian Liang 1, a, Ligang Hou 1, b and Jinhui Wang 2, c

VLSI and System Lab, Beijing University of Technology, Beijing 100124, China

Department of Electrical and Computer Engineering, North Dakota State University, ND 58102,USA

DCG에서는 DCT와 같은 방법으로 실행하고, def파일과 sdc파일을 갖고 Hotspot을 고려하는 Synthesis를 합니다.

아래 유저가이드에서, 어떻게 Congestion(Hotspot)을 해결하는지까지 나와있네요.

DCG 장점.

tsmc는 5nm공정까지 FinFET공정을 사용하고있고, 삼성전자는 7nm까지 FinFET을 쓰고 5nm부터는 GAA공정을 사용하고 있습니다.

앞으로 미세공정 기술이 깊어짐에따라, 배선 문제가 더 중요해질 것이고, Net delay의 비중은 더 커질 것입니다.

지금까지 DC -> DCT -> DCG로 왔던 것처럼 새로운 설계 기법이 나올 것입니다.