setup/hold개념처럼, PVT/OCV개념도 명확하게 남에게 설명하기란 쉽지 않았습니다. 그래서 재정리합니다.

우선, 칩은 Process (공정) / Voltage (전압) / Temperature (온도)에 관련하여 칩의 성능이 변화된다.

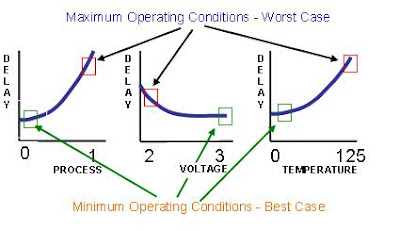

이해를 돕기 위해서, PVT가 칩의 속도에 어떻게 관여하는지 표나 그래프로 도식화한게 있긴한데, 공정마다 달라서.. 절대적인 것 아닙니다. 아래의 그래프를 보고 ‘아~ 대강 그렇구나’하고, 텍스트로 보고 이해하세요.

(1) 같은 기능을 하는 칩을 만들더라도, 5nm공정에서 만든 칩이 130nm공정에서 만든 칩보다 빠르게 동작한다. 왜냐하면 게이트 길이가 짧아서, 0->1, 1->0의 스위칭이 더 빠르게 일어나고.. 그 외에도 다양한 요인이 있다.

(2) Voltage는 낮게 걸어준 것보다, 세게 걸어준게 더 빠르게 동작한다. 쉽게 설명하면, 물레방아에 물을 세게 떨어뜨린다는 느낌… 물 한방울씩 떨어질땐 물레방아가 꿈쩍도 않다가, 어느정도 임계 수압을 가해줘야 물레방아가 돌고, 어느정도까진 수압에 비례해 물레방아가 빠르게 돌아간다. 너무 세면 물레방아가 망가지겠지.

(3) 온도가 높아지면, 소자들의 물성에 변화가 생깁니다. capacitance가 높아지고(스위칭 시간 길어짐), threshold값(스위칭 시간 짧아짐)이 내려갑니다. 0.18um공정까지는 capacitance의 영향이 컸는데, 더 미세공정으로 들어오면서 threshold의 영향이 커졌습니다. 그래서 과거엔 온도가 높으면 delay가 커지는, worst case로 봤는데, 현재는 온도가 낮을 때도 봐야합니다. 낮은 온도보다 높은 온도에서 빠르게 동작하는 것을 Timing inversion이나 Temperature inversion이라고 합니다.

이제 Process / Voltage / Temperature가 어떻게 칩의 성능에 관여하는지 봤어요. 근데 우리가 vlsi에서 말하는 pvt의 개념은 여기서 끝나는건 아니고,

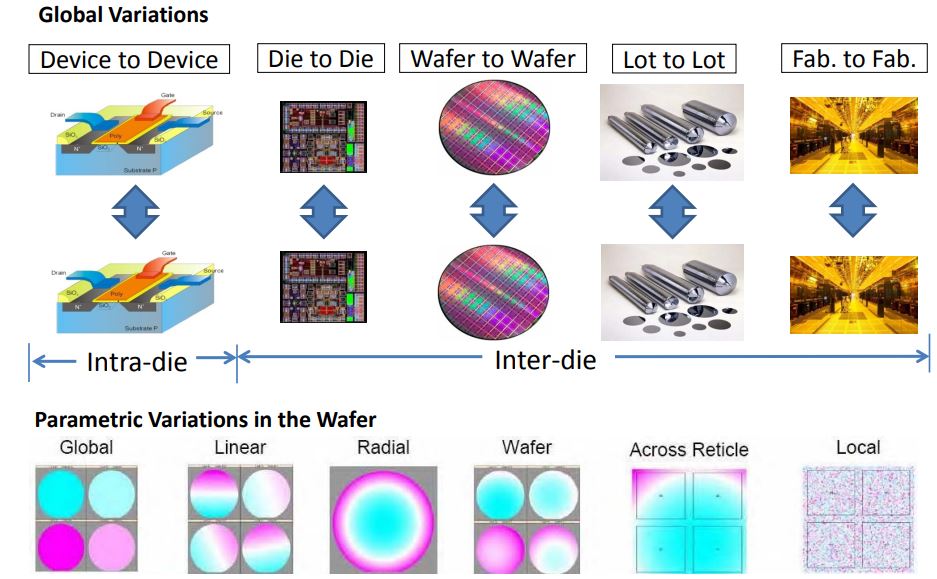

같은 공장의 같은 기계에서 수십 개의 칩들을 한 웨이퍼에 찍더라도, 웨이퍼 구석에 있는 칩과 중앙부의 칩의 실리콘 산화도가 미미하게 다를 수 있고, 어느 부분에는 도핑이 더 된 부분이 있을거에요. (근데 한 기계에서만 칩을 찍는 것이 아니고, 기계들간의 노후화 차이도 있을 것이고,,, 웨이퍼 자르고 잉곳 만드는 것의 차이까지 생각하면…. 모든 칩들은 다 미미하게 다른 물성을 갖게 됩니다.)

그래서 다이간의 물성 차이가 생기는데, Timing margin을 줘서, 약간의 perfomnce 차이가 생겨도 모든 칩이 동작 할 수 있도록 pvt를 신경써서 반도체 구현을 해야합니다.

OCV는 뭘까요? On Chip Variation. 칩 위에서 생기는 변화에 대해 마진을 주기위해 필요한 개념이에요.

손톱만한 한 칩 위에서도 차이가 있어요. 예를들어 한 칩 위의 A위치에는 선들이 복잡하게 이어져있고, B위치에는 선들이 거의 없다면, A 위치에 있는 셀들이 좀 더 쉽게 발열이 될 것 입니다. 이런 것들에… 대한 마진을 줘야해요.

그래서 Design compiler 같은 합성 Tool에선 sdc에서 operating condition과 ocv를 통해 Timing margin에 대한 정보를 알려줍니다.

ocv는 현재 ocv, aocv, pocv로 나누는데요. 그냥 ocv는 합성툴 런타임이 가장 빠르고, pocv가 가장 느리며 정확합니다. (그냥 OCV는 너무 worst하게 봐서, margin을 많이 주려고함.)

aocv는 칩의 공간내에 얼마나 많은 셀들이 있는지만 봐서, A위치에 생길 수 있는 worst case를 고려해 최대 margin을 줍니다.

pocv는 aocv와 비슷한데, 무조건 Worst case의 margin을 주는 것이 아니라, A위치에 생길 수 있는 모든 case들의 확률들을 계산해 정규분포를 통해 마진을 줍니다.

PVT와 OCV를 한번 봤습니다. 오개념 정리 다시 한번 하고 가겠습니다.

(1) 꼭 무조건 빠르게만 들어가면 해결되는건 아니고, 클럭 스피드를 기준으로 적정해야합니다. data path에서 max일때 worst인건 setup이지만, holdtime violation은 data path가 min일 때 worst하니까요.

(2) PVT의 V는 Chip에 공급되는 전압이 아니라, Cell에 공급되는 전압입니다. IR-Drop을 고려해야합니다.

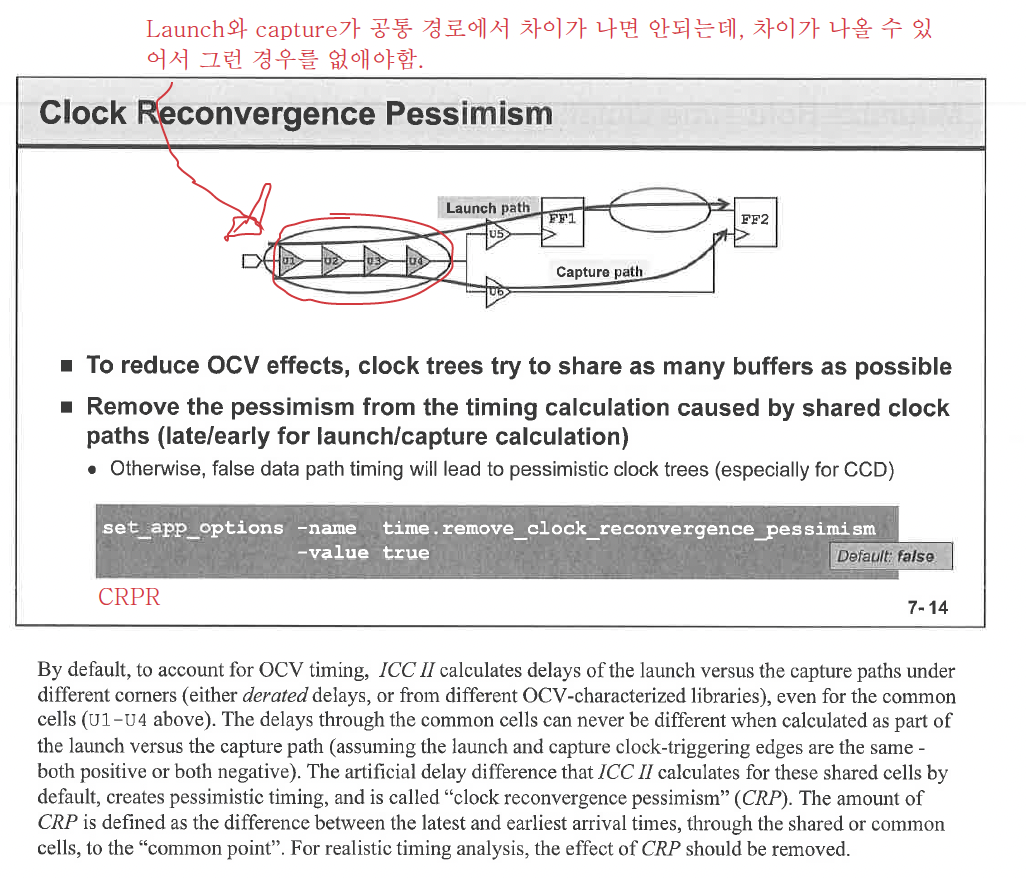

(3) CRPR, POCV synopsys사에서 쓰는 용어이고, CPPR, AOCV는 Cadence사에서 쓰는 용어임. 열어보면 계산하는 방법에 대해 차이가 존재하긴하지만, 둘 다 개념은 같음.

(4) PVT, OCV만 고려하먄 되나? 미세공정에선 PEX(parasitic extraction)도 고려해야됨.

Timing margin을 준다고 했어요. 한 path가 10ns 걸리는 것에 + - 10% 마진을 주면, 9ns~11ns가 걸릴 수 있다고 가정을 하는 것이에요.

우선, 한 순간의 한 경로에선 한가지 타이밍 특성을 가질 수 있어요. 그러나 툴에 이걸 알려주지 않는다면,

그림의 Launch path(Input Port ~ F/F1 ~ F/F2)에서 공통경로(Input ~ U4)에선 11ns가 걸리고, Capture path(Input Port ~ F/F2)에서 공통경로(Input ~ U4)에선 9ns가 걸린다고 하면.. capture F/F에서 일찍 클럭이 들어오는데, Launch단에서 데이터를 너무 늦게 보내서 Setup time violation이 생길 수 있어요.

실제로는 이런 일이 안 생기기 떄문에, 툴에 공통경로의 타이밍 차이를 제거해줘야한다고 얘기를 해줘야합니다. 이게 crpr입니다.